There is only one known route, a 5C from the landward side.[1]

References

- Climbing areas of Scotland

- Landforms of Orkney

- Stacks of Scotland

- Tourist attractions in Orkney

- Hoy

- Scotland geography stubs

- Climbing stubs

https://en.wikipedia.org/wiki/Needle_(stack)

In chemistry, pi stacking (also called π–π stacking) refers to the presumptive attractive, noncovalent pi interactions (orbital overlap) between the pi bonds of aromatic rings. However this is a misleading description of the phenomena since direct stacking of aromatic rings (the "sandwich interaction") is electrostatically repulsive. What is more commonly observed (see figure to the right) is either a staggered stacking (parallel displaced) or pi-teeing (perpendicular T-shaped) interaction both of which are electrostatic attractive[1][2] For example, the most commonly observed interactions between aromatic rings of amino acid residues in proteins is a staggered stacked followed by a perpendicular orientation. Sandwiched orientations are relatively rare.[3]

Pi stacking is repulsive as it places carbon atoms with partial negative charges from one ring on top of other partial negatively charged carbon atoms from the second ring and hydrogen atoms with partial positive charges on top of other hydrogen atoms that likewise carry partial positive charges.[1] In staggered stacking, one of the two aromatic rings is offset sideways so that the carbon atoms with partial negative charge in the first ring are placed above hydrogen atoms with partial positive charge in the second ring so that the electrostatic interactions become attractive. Likewise, pi-teeing interactions in which the two rings are oriented perpendicular to either other is electrostatically attractive as it places partial positively charged hydrogen atoms in close proximity to partially negatively charged carbon atoms. An alternative explanation for the preference for staggered stacking is due to the balance between van der Waals interactions (attractive dispersion plus Pauli repulsion).[4]

These staggered stacking and π-teeing interactions between aromatic rings are important in nucleobase stacking within DNA and RNA molecules, protein folding, template-directed synthesis, materials science, and molecular recognition. Despite the wide use of term pi stacking in the scientific literature, there is no theoretical justification for its use.[1]

https://en.wikipedia.org/wiki/Stacking_(chemistry)

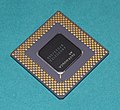

A pin grid array (PGA) is a type of integrated circuit packaging. In a PGA, the package is square or rectangular, and the pins are arranged in a regular array on the underside of the package. The pins are commonly spaced 2.54 mm (0.1") apart,[1] and may or may not cover the entire underside of the package.

PGAs are often mounted on printed circuit boards using the through hole method or inserted into a socket. PGAs allow for more pins per integrated circuit than older packages, such as dual in-line package (DIP).

Chip mounting

The chip can be mounted either on the top or the bottom (the pinned side). Connections can be made either by wire bonding or through flip chip mounting. Typically, PGA packages use wire bonding when the chip is mounted on the pinned side, and flip chip construction when the chip is on the top side. Some PGA packages contain multiple dies, for example Zen 2 and Zen 3 Ryzen CPUs for the AM4 socket.

Flip chip

A flip-chip pin grid array (FC-PGA or FCPGA) is a form of pin grid array in which the die faces downwards on the top of the substrate with the back of the die exposed. This allows the die to have a more direct contact with the heatsink or other cooling mechanism.

The FC-PGA was introduced by Intel with the Coppermine core Pentium III and Celeron[2] processors based on Socket 370, and was later used for Socket 478-based Pentium 4[3] and Celeron processors. FC-PGA processors fit into zero insertion force (ZIF) Socket 370 and Socket 478-based motherboard sockets; similar packages have also been used by AMD. It is still used today[when?] for mobile Intel processors.

Material

Ceramic

A ceramic pin grid array (CPGA) is a type of packaging used by integrated circuits. This type of packaging uses a ceramic substrate with pins arranged in a pin grid array. Some CPUs that use CPGA packaging are the AMD Socket A Athlons and the Duron.

A CPGA was used by AMD for Athlon and Duron processors based on Socket A, as well as some AMD processors based on Socket AM2 and Socket AM2+. While similar form factors have been used by other manufacturers, they are not officially referred to as CPGA. This type of packaging uses a ceramic substrate with pins arranged in an array.

A 1.2 GHz VIA C3 microprocessor in a ceramic package

Organic

An organic pin grid array (OPGA) is a type of connection for integrated circuits, and especially CPUs, where the silicon die is attached to a plate made out of an organic plastic which is pierced by an array of pins which make the requisite connections to the socket.

The underside of a Celeron-400 in a PPGA

Plastic

Plastic pin grid array (PPGA) packaging was used by Intel for late-model Mendocino core Celeron processors based on Socket 370.[4] Some pre-Socket 8 processors also used a similar form factor, although they were not officially referred to as PPGA.

Pin layout

Staggered pin

The staggered pin grid array (SPGA) is used by Intel processors based on Socket 5 and Socket 7. Socket 8 used a partial SPGA layout on half the processor.

It consists of two square arrays of pins, offset in both directions by half the minimum distance between pins in one of the arrays. Put differently: within a square boundary the pins form a diagonal square lattice. There is generally a section in the center of the package without any pins. SPGA packages are usually used by devices that require a higher pin density than what a PGA can provide, such as microprocessors.

Stud

A stud grid array (SGA) is a short-pinned pin grid array chip scale package for use in surface-mount technology. The polymer stud grid array or plastic stud grid array was developed jointly by the Interuniversity Microelectronics Centre (IMEC) and Laboratory for Production Technology, Siemens AG.[5][6]

rPGA

The reduced pin grid array was used by the socketed mobile variants of Intel's Core i3/5/7 processors and features a reduced pin pitch of 1 mm,[7] as opposed to the 1.27 mm pin pitch used by contemporary AMD processors and older Intel processors. It is used in the G1, G2, and G3 sockets.

See also

- Ball grid array (BGA)

- Centered square number

- Chip carrier - chip packaging and package types list

- Dual in-line package (DIP)

- Land grid array (LGA)

- Single in-line package (SIP)

- Zig-zag in-line package (ZIP)

References

{{cite web}}: Missing or empty |url= (help)

- "Molex Sockets for Servers, Desktops and Notebooks Earn Intel® Validation". Retrieved 2016-03-15.

Sources

- Thomas, Andrew (August 4, 2010). "What the Hell is… a flip-chip?". The Register. Retrieved December 30, 2011.

- "XSERIES 335 XEON DP-2.4G 512 MB". CNET. October 26, 2002. Retrieved December 30, 2011.

- "SURFACE MOUNT NOMENCLATURE AND PACKAGING" (PDF).

External links

- Intel CPU Processor Identification

- Ball Grid Arrays: the High-Pincount Workhorses[permanent dead link], John Baliga, associate editor, Semiconductor International, 9/1/1999

- Spot on component packaging[permanent dead link], 08/1998, Elektronik, Produktion & Prüftechnik

- Terminology

https://en.wikipedia.org/wiki/Pin_grid_array

Pinnipeds (pronounced /ˈpɪnɪˌpɛdz/), commonly known as seals,[a] are a widely distributed and diverse clade of carnivorous, fin-footed, semiaquatic, mostly marine mammals. They comprise the extant families Odobenidae (whose only living member is the walrus), Otariidae (the eared seals: sea lions and fur seals), and Phocidae (the earless seals, or true seals). There are 34 extant species of pinnipeds, and more than 50 extinct species have been described from fossils. While seals were historically thought to have descended from two ancestral lines, molecular evidence supports them as a monophyletic lineage (descended from one ancestral line). Pinnipeds belong to the order Carnivora; their closest living relatives are musteloids (weasels, raccoons, skunks, and red pandas), having diverged about 50 million years ago.

https://en.wikipedia.org/wiki/Pinniped

| Pine Temporal range:

| |

|---|---|

| |

| Korean red pine (Pinus densiflora), North Korea | |

| Scientific classification | |

| Kingdom: | Plantae |

| Clade: | Tracheophytes |

| Clade: | Gymnosperms |

| Division: | Pinophyta |

| Class: | Pinopsida |

| Order: | Pinales |

| Family: | Pinaceae |

| Subfamily: | Pinoideae |

| Genus: | Pinus L. |

| Type species | |

| Pinus sylvestris | |

| Subgenera | |

|

See List of Pinus species for complete taxonomy to species level. See list of pines by region for list of species by geographic distribution. | |

| |

| Range of Pinus | |

| Synonyms | |

| |

A pine is any conifer tree or shrub in the genus Pinus (/ˈpiːnuːs/)[1] of the family Pinaceae. Pinus is the sole genus in the subfamily Pinoideae. The World Flora Online created by the Royal Botanic Gardens, Kew and Missouri Botanical Garden accepts 187 species names of pines as current, together with more synonyms.[2] The American Conifer Society (ACS) and the Royal Horticultural Society accept 121 species. Pines are commonly found in the Northern Hemisphere. Pine may also refer to the lumber derived from pine trees; it is one of the more extensively used types of lumber. The pine family is the largest conifer family and there are currently 818 named cultivars (or trinomials) recognized by the ACS.[3]

https://en.wikipedia.org/wiki/Pine

A pin is a device used for fastening objects or fabrics together and can have three sorts of body: a shaft of a rigid inflexible material meant to be inserted in a slot, groove, or hole (as with pivots, hinges, and jigs); a shaft connected to a head and ending in a sharp tip meant to pierce one or more pieces of soft materials like cloth or paper (the straight or push pin); a single strip of a rigid but flexible material (e.g. a wire) whose length has been folded into parallel prongs in such fashion that the middle length of each curves towards the other so that, when anything is inserted between them, they act as a clamp (e.g. the bobby pin), or two strips of a rigid material bound together by a spring at one end so that, when the spring held open, one can insert some material between the prongs at the other end that, the spring allowed to close, then clamp the inserted material. According to their function, pins can be made of metals (e.g. steel, copper, or brass), wood, or plastic.

https://en.wikipedia.org/wiki/Pin

https://en.wikipedia.org/wiki/Solid_pin

Core inflation represents the long run trend in the price level. In measuring long run inflation, transitory price changes should be excluded. One way of accomplishing this is by excluding items frequently subject to volatile prices, like food and energy.

https://en.wikipedia.org/wiki/Core_inflation

The PCE price index (PePP), also referred to as the PCE deflator, PCE price deflator, or the Implicit Price Deflator for Personal Consumption Expenditures (IPD for PCE) by the Bureau of Economic Analysis (BEA) and as the Chain-type Price Index for Personal Consumption Expenditures (CTPIPCE) by the Federal Open Market Committee (FOMC), is a United States-wide indicator of the average increase in prices for all domestic personal consumption. It is benchmarked to a base of 2012 = 100. Using a variety of data including U.S. Consumer Price Index and Producer Price Index prices, it is derived from the largest component of the GDP in the BEA's National Income and Product Accounts, personal consumption expenditures.

https://en.wikipedia.org/wiki/Personal_consumption_expenditures_price_index

The Central Organisation for Railway Electrification (CORE) is the unit of Indian Railways responsible for electrification of the network. The organisation, founded in 1979,[1] is headquartered in Prayagraj, Uttar Pradesh. Project units operate in Ambala, Bangalore, Chennai, Secunderabad, Lucknow, Ahmedabad, Jaipur, Danapur, and New Jalpaiguri.

CORE headquarters has Electrical, Signal and Telecommunications (S&T), Civil Engineering, Stores, Personnel, Vigilance and Finance departments. Railway Electrification project units are headed by Chief Project Directors.

Indian Railways had electrified 58,812 route kilometres (RKM) which is about 90% of the total broad gauge network of Indian Railways (65,300 RKM, including Konkan Railway) by 1 April 2023.[2] Indian Railway aims to electrify all of its broad gauge network by 31 March 2024.[3] The entire electrified mainline rail network in India uses 25 kV AC; DC is used only for metros and trams.

https://en.wikipedia.org/wiki/Central_Organisation_for_Railway_Electrification

In computing, autonomous peripheral operation is a hardware feature found in some microcontroller architectures to off-load certain tasks into embedded autonomous peripherals in order to minimize latencies and improve throughput in hard real-time applications as well as to save energy in ultra-low-power designs.

https://en.wikipedia.org/wiki/Autonomous_peripheral_operation

Overview

Forms of autonomous peripherals in microcontrollers were first introduced in the 1990s. Allowing embedded peripherals to work independently of the CPU and even interact with each other in certain pre-configurable ways off-loads event-driven communication into the peripherals to help improve the real-time performance due to lower latency and allows for potentially higher data throughput due to the added parallelism. Since 2009, the scheme has been improved in newer implementations to continue functioning in sleep modes as well, thereby allowing the CPU (and other unaffected peripheral blocks) to remain dormant for longer periods of time in order to save energy. This is partially driven by the emerging IoT market.[1]

Conceptually, autonomous peripheral operation can be seen as a generalization of and mixture between direct memory access (DMA) and hardware interrupts. Peripherals that issue event signals are called event generators or producers whereas target peripherals are called event users or consumers. In some implementations, peripherals can be configured to pre-process the incoming data and perform various peripheral-specific functions like comparing, windowing, filtering or averaging in hardware without having to pass the data through the CPU for processing.

https://en.wikipedia.org/wiki/Autonomous_peripheral_operation

See also

- Channel I/O

- Peripheral DMA controller (PDC)

- Clock gating, autonomous peripheral clock gating

- Power gating

- CPU power dissipation

- Low-power electronics

- Event-driven architecture

- Event-driven programming

- Always On, Always Connected (AOAC)

- Energy-Efficient Ethernet (EEE)

- TCP offload engine (TOE)

References

[…] Drives need realtime performance – control loop must run faster than 2-4 PWM periods (e.g. 100-200us) – CPU performance is valuable and must be saved for key tasks – Question: How to offload the CPU? –Answer: Build intelligent and autonomous peripherals! […] CC6 in a Drive application: – generate PWM patterns for all kind of motors – operate always in a safe state – even in an error condition – interact with ADC for sensorless control of motors […] CC6 is used intensively – the more it works autonomous the more CPU load can be saved for control algorithms […]

- "Peripherals interconnections on ST M32F405/7xx, STM32F415/7xx, STM32F42xxx, STM32F43xxx, STM32F446xx and STM32F469/479xx" (PDF) (Application note). STMicroelectronics. AN4640. Archived (PDF) from the original on 2018-05-01. Retrieved 2018-05-01.

https://en.wikipedia.org/wiki/Autonomous_peripheral_operation

Category:Central processing unit

Subcategories

This category has the following 6 subcategories, out of 6 total.

+

- Macintosh computers by CPU family (4 C, 1 P)

C

- CPU sockets (2 C, 10 P)

L

- Logic families (40 P)

M

- Microprocessors (24 C, 25 P)

Pages in category "Central processing unit"

The following 80 pages are in this category, out of 80 total. This list may not reflect recent changes.

A

C

H

M

P

S

https://en.wikipedia.org/wiki/Category:Central_processing_unit

No comments:

Post a Comment